#### **Abstract Authors**

A new interleaved high gain boost Albiva Sara Eldhose converter is suggested for renewable energy Department of EEE application. By amalgamating coupled- College of Engineering inductor and switched capacitor boosting MunnarMunnar, Kerala, techniques, the suggested interleaved boost India converter accomplishes very high step-up voltage gain unaccompanied by high turns Dr. Biju K ratio and extreme duty cycle. Though a HOD classic DC-DC Boost converter can furnish Department of EEE a high output voltage with a smaller duty ratio, low efficiency and switch voltage stress are the shortcomings. Here in this interleaved boost converter by adopting the low-voltage rated switches and small RDS (On), the voltage stress of the switches is inferior than the output voltage. Also the efficiency of the converter have heightened. Thus two drawbacks of classic boost eliminated here. The converter is experimental results, using a prototype of 18V/400V, corroborate the efficacious performance of suggested converter.

Keywords: Coupled inductor, High gain boost converter, Interleaved, Switched capacitor.

College of Engineering Munnar Munnar, Kerala, India

#### I. INTRODUCTION

In electrical and electronics engineering, power electronics associates with the processing of high voltages and currents to deliver power that aids a variety of needs. Over the last few years, heed to power electronic equipment has elevated tremendously. Another interesting fact is that the consciousness towards renewable energy sources (eg: Solar energy) also heightened due to the environmental problems prompted by fossil fuels and global warming. The main snag of these power sources is that they lack the potentiality to generate high DC voltage. For that reason the need to use the power electronic equipment (ie:Power electronic converters) has maximized more than before. Together with escalating growth of renewable power, the power electronic converters have also undergone changes in structure and design to increase performance and efficiency. Long ago a traditional DC-DC boost converter were used as power electronic converters in photovoltaic (PV) systems. The prime merit of this typical boost converter is that its simple structure. Their elevated voltage stress, low power density, reverse recovery problem, output voltage sensitivity to the duty cycle and high current ripple are the stumbling blocks. The DC voltage in step-up DC-DC converter increases mainly by storing energy at the input side and releasing it towards the output [1]. Fundamentally, such converters are divided into non isolated and isolated types [2]. The flyback converters [4]-[5] and the forward converters [6]-[7] are examples of this categorization. The non isolated converters are unification of conventional DC-DC converter and voltage boosting techniques. The switched capacitors [8]-[11], the switched inductors [12]-[14], the voltage multipliers [15], the coupled inductors [16]-[19] and multiphase converter topology (ie: Interleaved) are among the preeminent voltage boosting methods. When coupled inductors are used, the main advantage is that the number of magnetic cores will definitely decrease. Switched inductor and switched capacitors boosting techniques are the combination of diodes- inductors and diodes-capacitors respectively. At the present time, the prime focus of researchers are on mitigating the problems arose by expanding the voltage gain in newer converter topologies. The predicaments of these topologies are voltage stress of semiconductors, lower efficiency, current ripple, lack of soft- switching conditions. The voltage boosting techniques switched capacitor/switched coupled inductors are described detail in [20]. Here in this converter the magnitude of stress arose is low. In [21] a high boost Dc-Dc converter structure composed of switched capacitors and coupled inductors is introduced and explained. The main defect of this converter is that the vulnerability of its voltage gain towards duty cycle.

This chapter suggests a novel high gain boost converter in the company of an interleaved structure and a network comprising of coupled inductors and switched capacitor cells. The chief contributions of this study are,

- The voltage conversion ratio get increased.

- The converter have very low switch voltage stress. (iii)It has high efficiency.

- Its input current ripple is remarkably diminished.

#### II. PROPOSED CONVERTER STRUCTURE

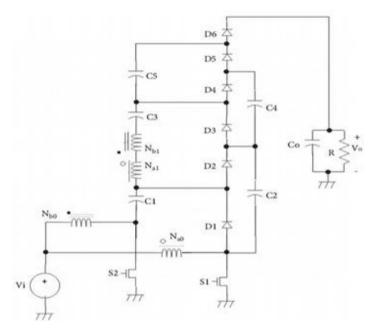

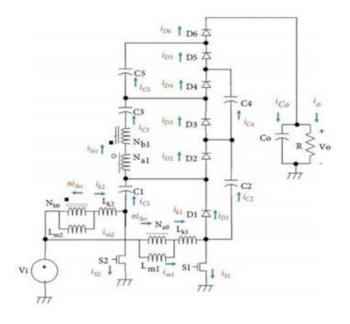

Figure 1 shows a two phase interleaved boost converter [24]. Its circuit components are grouped into three stages. Its input stage comprised of two coupled inductors and two power switches (S1 and S2). In the middle stage, it has five capacitors (C1-C5) and six diodes

(D1- D6) as energy transfer. Finally, the output stage contain the output capacitor (**Co**) and the load (R). In order to accomplish ultra high voltage gain, two sets of switched capacitor networks were placed back to back. Figure 2 illustrates the equivalent circuit of the suggested structure. The adopted duty cycle ratio is 0.55. Here the proposed converter has principally four operation modes.

Figure 1: Power circuit of interleaved boost converter

- 1. Operation Principles: Consider the following assumptions:

- The circuit components employed are ideal.

- Large capacitors are used.

Figure 2: Equivalent circuit

Figure 3: Key waveforms in CCM operation

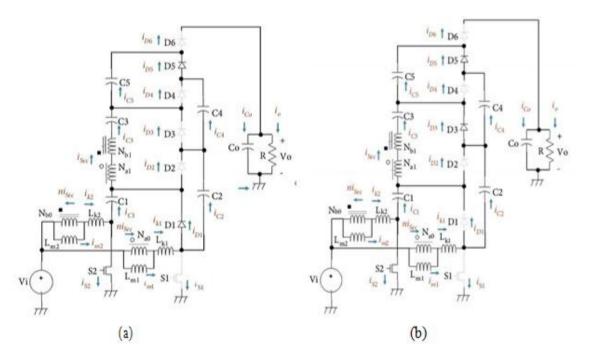

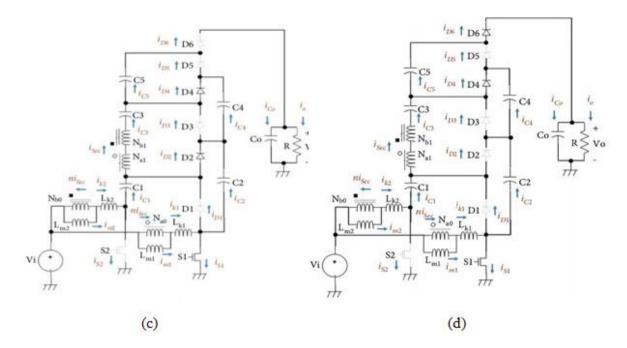

1. Mode 1 [t0-t1]: At t0, S1 is turned off. D1 and D5 conduct. Lk2 and Lm2 are charged through the input. The leakage current ik1, charges C1 and other capacitors are swapping energy. iD1 is decreased.

$$Vm1 = Vi - VC1 \tag{1}$$

$$Vm2=Vi$$

(2)

2. Mode 2 [t1-t2]: iD1 decreases linearly in the previous mode. This current turns into zilch at t1 and D1 turns off naturally according to Figure 4(b). In this mode D3 starts to conduct.

$$Vi = VC1 - VC2 + VC3 - n (Vm2 - Vm1) + Vm1 Vm2 = Vi$$

(3)

**3.** Mode 3 [t2-t3]: S2 is turned off at t2 as shown in Figure 4(c). D2 and D4 conduct. Lk1 and Lm1 are get charged. Here C3 act as a voltage source. iD2 is decreased. Thus C2 is charged.

$$Vm1 = Vi$$

(4)

$$Vm2 = Vi + VC1 - VC2$$

(5)

**4. Mode 4 [t3-t0]:** iD2 becomes zero at t3. D2 is turned off naturally according to Figure 4(d). In this mode D6 starts to conduct.

$$Vi = Vo + Vm2 - VC1 - VC3 - VC5 - n(Vm1 - Vm2)$$

(6)

#### III. STEADY-STATE ANALYSIS

**1. Voltage Gain:** By applying volt-second balance principle, the following equations are expressed:

$$V^{on} D T + V^{off} (1 - D) T = 0$$

$$V_i D T + (V_i - V_{C1}) (1 - D) T = 0$$

(7)

Here D and T implies duty cycle ratio and switching period respectively. From equation (15), the voltage of C1 earned is,

$$V_{C1} = \frac{1}{\left(1 - D\right)^{V}}$$

(8)

Using (16) and (17), the voltage obtained for C2 is,

$$V_{C2} = \frac{2}{\left(1 - D\right)} V_i \tag{9}$$

Using equations (1)–(18), the voltage of C3 is,

$$V_{C3} = \frac{n+2}{(1-D)} V_i$$

(10)

Using equations (6)–(8) and (13) to (14), the voltage of C4 is obtained as follows:

$$v_{L4} - \frac{2n+2}{(1-D)}v_L$$

(11)

Thus, using (7),

$$V_{2} = \frac{2n+2}{(1-D)} V_{1}$$

(12)

Using equations (11), (13), (17), (18), (19) and (21), the voltage gain earned is,

$$M = \frac{Vo}{V_i}$$

$$=\frac{(4n+6)}{(1-D)} \tag{13}$$

Figure 4: Circuits corresponding to the operation modes: (a) mode 1 [t0-t1]; (b) mode 2 [t1t2]; (c) mode 3 [t2-t3]; (d) mode 4 [t3-t0].

2. Voltage Stress: For capacitors, the equations of voltage stress are,

$$V_{C1} = \frac{1}{4n+6} V_{o}$$

$$V_{C2} = \frac{2}{(4n+6)} V_{o}$$

$$V_{C3} = \frac{n+2}{4n+6} V_{o}$$

$$V_{C4} = V_{C5} = \frac{2n+2}{4n+6} V_{o}$$

(14)

The voltage stress of the switches are,

$$V_{S1} = V_{S2}$$

$$= \frac{1}{1-D} V_i$$

$$- \frac{1}{4n+6} V_0$$

(15)

Hence when n=1, voltage stress equations are one-tenth of the output voltage (ie: conduction losses in the proposed converter are decreased with a small RDS(on)).

For diodes, the voltage stress equations are,

$$V_{D1} = V_{D2}$$

=  $|-V_{C2}|$

=  $\frac{2}{4n+6}V_{Q}$

$$V_{D3} = V_{D4}$$

$$= | -V_{C4}|$$

$$-\frac{2n+2}{4n+6}v_{o}$$

$$V_{D6} = |V_{C1} + V_{C3} + V_{C5} + V_{o}|$$

$$-\frac{n+1}{4n+6}v_{o}$$

(16)

3. Input Current Ripple and magnetizing Inductance: Here the current gain is,

$$\frac{I_0}{I_i} \langle Avg \rangle = \frac{1-D}{4n+6}$$

(17)

Let Im1\_Avg and Im2\_Avg are average magnetizing currents, then they are narrated by the following equation with the support of the equation (26),

$$Im1\_Avg = Im2\_Avg$$

$$= Im \_Avg$$

$$= \frac{l_{\underline{i}} Avg}{2}$$

$$= \frac{2n+3}{(1-D)} r_{0\_}^{\underline{i}} Avg$$

(18)

The input current is,

$$i_i = (i_{m1} + ni_{Sec}) + (i_{m2} - ni_{Sec})$$

=  $i_{m1} + i_{m2}$  (19)

The ripple of the input and magnetizing currents is,

$$\Delta i_{\rm m} = \frac{D}{L_{\rm m} f_{\rm s}} V_{ij} \tag{20}$$

$$A: \frac{2D-1}{i} \frac{V}{L_m f_s} \frac{V}{i} \tag{21}$$

### IV. THE DESIGN OF CONVERTER COMPONENTS

1. Coupled Inductors: Select a duty ratio cycle (D) greater than 0.5. Here the turns ratio is,

$$n = \frac{M(1-D)-6}{4} \tag{22}$$

The magnetizing inductances are,

$$\begin{split} L_{m1} &= L_{m2} \\ &= L_{m} \\ &= \frac{D.Vi}{\Delta imfs} \end{split} \tag{23}$$

IIP Series, Volume 3, Book 1, Part 6, Chapter 3

AN INTERLEAVED HIGH GAIN BOOST CONVERTER FOR RENEWABLE ENERGY APPLICATION

Prime condition should be satisfied is that  $Im\_Avg > \frac{1}{2}$ .  $\Delta im$ . Thus, the minimum magnetizing inductance is,

$$Lm > \frac{1}{2} \frac{(1-D)D.Vi}{(2n+3)Io\_Avgfs}$$

(24)

The leakage inductance are,

$$= \frac{(n+1)Vo}{4(2n+3)x} \cdot \frac{diD3(t)}{dt} = x$$

(25)

Considering (27) and (29), peak magnetizing currents are gained as follows,

$$Im1_Pk = Im2_Pk$$

$$= Im_Pk$$

$$-\frac{2n+3}{(1-D)}I_{Avg} \cdot \frac{1}{2}\frac{D.Vi}{Lmfs}$$

(26)

2. Semiconductors: Average current of all diodes is,

$$ID1\_Avg$$

,...,  $ID6\_Avg = Io Avg$ . (27)

According to equation (38), the diode's peak current are earned by arranging the equation (37) as follows:

Io Avg =

$$\frac{1}{2}$$

(ID1 Pk...ID6 Pk)(1 – D) (28)

ID1 Pk...ID6 Pk =

$$\frac{2.\text{Io Avg}}{(1-D)}$$

(29)

The peak current of the power switches are,

$$IS1\_Pk \simeq \frac{Ii\_Avg}{2} + ID2\_Pk + nID4\_Pk = \frac{(4n+5)Io\_Avg}{(1-D)}$$

$$IS2\_Pk \simeq \frac{Ii\_Avg}{2} + nID3\_Pk + nID\_Pk = \frac{(6n+3)Io\_Avg}{(1-D)}$$

(30)

By the equation (27) and considering the operating modes the RMS current of the switches are,

IS1 RMS=

$$\frac{(2n+3)\log_{A} \log}{(1-D)} \left(\sqrt{(1-2D) - \frac{4(1-D)(n^3+3n^2+3n+1)}{n^3+4n^2+5n+2}}\right)$$

(31)

IS2\_RMS =

$$\frac{(2n+3)Io\_Avg}{(1-D)}(\sqrt{3-2D})$$

(32)

**3.** Capacitors: The design equations of capacitors are,

$$C1 = \frac{4n+6}{\Delta V c V_0^2 f s}$$

$$C2 = \frac{(2n+3)Po}{\Delta V c V_0^2 f s}$$

$$C3 = \frac{(4n+6)Po}{(n+2)\Delta V c V_0^2 f s}$$

$$C4 = C5 = \frac{(2n+3)Po}{(n+1)\Delta V c V_0^2 f s}$$

(33)

#### V. COMPARISON

Table 1 compares the suggested converter with other converters that are similar in topology and structure. The number of switches and number of magnetic cores used in suggested converter are same as that of the converters in [24] and [25]. Also the efficiency get increased in this converter by 96.6%.

Table 1: Comparison of the suggested converter with similar converters

| Topologies | Voltage<br>gain    | S | D | C | M | Efficiency (%) |

|------------|--------------------|---|---|---|---|----------------|

|            | (2N + 4)           | 2 | 4 | 4 | 2 | 94.9           |

| [24]       | (1-D)              |   |   |   |   |                |

|            | (4N + 4)           | 2 | 4 | 4 | 2 | 94.5           |

| [25]       | (1 - D)            |   |   |   |   |                |

|            | (4N + 6)           | 2 | 6 | 6 | 2 | 96.6           |

| Proposed   | $\overline{(1-D)}$ |   |   |   |   |                |

S No. of power switches; D − No. of diodes;

C − No. of capacitors; M − No. of magnetic cores.

#### VI. SIMULATION RESULTS

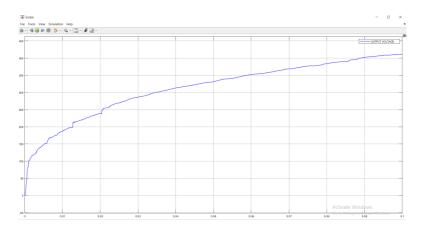

The suggested system was simulated in MATLAB/Simulink. Table 2 shows the simulation design parameters and its values. The magnetizing and leakage inductances are  $100\mu H$  and  $2.5\mu H$  respectively. The capacitors used are 20, 10, 7, 5, 5 and  $2*56\mu F$ . The duty cycle ratio (D) is 0.55.

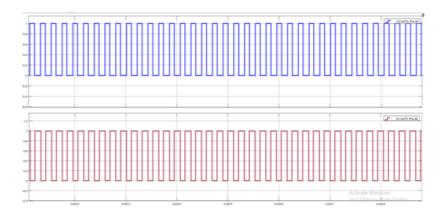

Figure 5 and Figure 6 shows the output voltage obtained from this interleaved boost converter (Vout) and the waveform of gate pulses of the switches S1 and S2. The output voltage obtained from this converter is 22.22 times the input voltage.

**Table 2: Simulation parameters**

| No. | Parameters                                     | Values                       |

|-----|------------------------------------------------|------------------------------|

| 1   | Input voltage                                  | 18V                          |

| 2   | Output voltage                                 | 400V                         |

| 3   | Magnetizing and Leakage inductances (Lmand Lk) | 100 μH and 2.5 μH            |

| 4   | Capacitors                                     | 20, 10, 7, 5, 5 and 2*56 μ F |

| 5   | Turns ratio                                    | 1:1                          |

Figure 5: Output voltage obtained from the simulation circuit

Figure 6: Gate pulses

### VII. EXPERIMENTAL RESULTS

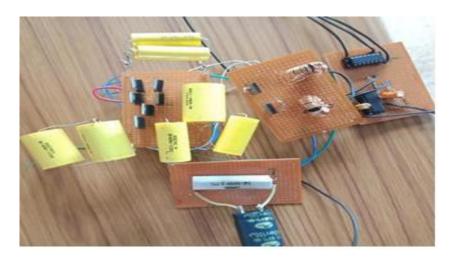

A 18V/400V interleaved boost converter was constructed. The main specifications of the prototype is given in Table 3. The sampling time is 21 microseconds. Value of n taken for coupled inductors are 1 and each winding comprises of 32 number of turns. MOSFETs employed are IPB072N15N3G and Schottky diodes (MBR40250 and MBR20150) are utilized to implement the prototype of suggested converter. The duty cycle is 0.55. The measured maximum efficiency of the converter is 96.6%.

| Tabl | ما | 3. | C | neci | fic | ations |   |

|------|----|----|---|------|-----|--------|---|

| Lan  | ı  | J. | O | Deci | HU  | auons  | • |

| Parameters                        | Description                 |

|-----------------------------------|-----------------------------|

| Input voltage, Vi                 | 18 V                        |

| Output voltage, Vo                | 400 V                       |

| Switching frequency, fs           | 47kHZ                       |

| Capacitors(C1,C2,C3,C4,C5 and Co) | 5, 5, 7, 20, 10 and 2*56 μF |

| Inductances (Lm and Lk)           | 100 μH and 2.5μH            |

| Turns ratio                       | 1:1                         |

| Diodes(D3,D4 and D5)              | MBR40250                    |

| Diodes(D1,D2 and D6)              | MBR20150                    |

| Power switches (S1 and S2)        | IPB072N15N3G                |

Figure 7: Experimental set-up

#### VIII. CONCLUSION

The suggested interleaved boost converter is a unification of two coupled inductors and switched capacitor boosting techniques. Its benefits are high voltage gain, high efficiency (96.6%), conduction loss is low in magnitude due to the use of advanced power switches and low converter loss. The results obtained from simulation circuit and prototype unveiled the efficacy of the suggested interleaved boost converter.

## **REFERENCES**

- [1] Y. B. M Hasaneen and Adel A. Elbaset Mohammed, "Design and Simulation of DC/DC Boost Converter.",pp. 335-340, 2008.

- [2] M. S. Bhaskar, V. K. Ramachandaramurthy, S. Padmanaban et al., "Survey of DC-DC non-isolated topologies for unidirectional power flow in fuel cell vehicles," IEEE Access, vol. 8,pp. 178130–178166, 2020.

- [3] S. Farhani, E. M. Barhoumi, and F. Bacha, "Design and hardware investigation of a new configuration of an isolated DC-DC converter for fuel cell vehicle," Ain Shams Engineering Journal, vol. 12, no. 1, pp. 591–598, 2021.

- [4] T. F. Megahed, "Increasing efficiency and power factor for power supplies using parallel Flyback converter," Journal of Electrical Engineering & Technology, vol. 16, no. 1, pp. 155–169, 2021.

- [5] K. Raman, K. Jeyaraman, S. Mekhilef, and L. G. Alexander, "Design and stability analysis of interleaved Flyback converter control using Lyapunov direct method with FPGA implementation," Electrical Engineering, vol. 102, no. 3,pp. 1651–1665, 2020.

- [6] D. Habumugisha, S. Chowdhury and S.P Chowdhury, "A DC-DC Interleaved Forward converter to step-up DC voltage for DC Microgrid Applications", pp. 1-5, 2013.

- [7] Nagesh L. Bhanuprakash CV, B.K Singh and Vinod Chippalakatti, "Design and Implementation of Triple Output Forward DC-DC Converter with Coupled Inductor as Post-regulator for Space Application, pp. 175-179, 2020.

- [8] D. Sivaraj and M. Arounassalame, "High Gain Quadratic Boost Switched Capacitor Converter for photovoltaic Applications", pp. 1234-1239, 2017.

- [9] Oded Adutbul, Amir Gherlitz, Yefim Berkovich and Adrian Ioinovici, "Boost Converter with High Voltage Gain Using a Switched capacitor Circuit", pp. 296-299, 2019.

- [10] Jyotheeswara Reddt K and Sudhakar N, "High Voltage Gain Switched Capacitor Boost Converter with ANFIS Controller for Fuel Cell Electric Vehicle Application", pp. 465-470, 2018.

- [11] Minh-Khai Nguyen, Truong-Duy Duong and Young-Cheol Lim "Switched-Capacitor- Based Dual-Switch High-Boost DC-DC Converter", pp. 1-21, 2016.

- [12] Mahajan Sagar Bhaskar, Sanjeevikumar Padmanaban, Frede Blaabjerg and Patrick William Wheeler, "An Improved Multistage Switched Inductor Boost Converter (Improved M-SIBC) for Renewable Energy Applications: A key to Enhance Conversion Ratio,", pp. 1-6, 2018.

- [13] Mostafa Mousa, Mahrous Ahmed and Mohamed Orabi, "A Switched Inductor Multilevel Boost Converter", IEEE International Conference on Power and Energy, pp. 819-823, 2016.

- [14] Omar Abdel-Rahim, Mohamed Orabi, Emad Abdelkarim, Mahrous Ahmed and Mohamad Z. Yousaff, "Switched Inductor Boost Converter for PV Applications", IEEE Access, pp. 2100-2106, 2021.

- [15] M. Prudente L, L. Pfitscher and R. Gules, "A Boost Converter with Voltage Multiplier Cells,", IEEE Access, pp. 2716-2721, 2005.

- [16] Ian Laird, Dylan Dah-Chuan Lu and Vassilios G. Agelidis, "High-Gain Switched- Coupled-Inductor Boost Converter,",IEEE PEDS2009, pp. 423-428, 2009.

- [17] Haleh Jahangiri, Saeid Mohammadpour and Ali Ajami, "A High Step-Up DC-DC Boost Converter with Coupled inductor Based on Quadratic converters", IEEE 9th Annual Power Electronics, Drive Systems and Technologies Conferences (PEDSTC), pp. 20-25, 2018.

- [18] Felinto S.F. Silva, Antonio A.A Freitas, Sergio Daher, Saulo C. Ximenes, Sarah K.A. Sousa, Edilson M.S.Jr., Fernando L.M. Antunes and Cicero M.T. Cruz, "High Gain DC- DC Boost converter with a coupling inductor", pp. 486-492, 2009.

- [19] Moon-Hwan Keum, Yoon Choi and Sang-Kyoo Han, "High Efficiency Voltage- Clamped-inductor Boost converter", pp. 828-833, 2013.

- [20] S. Sadaf, S. Bhaskar, M. Meraj, A. Iqbal, and N. Al-Emadi, "A novel modified switched inductor boost converter with reduced switch voltage stress," IEEE Transactions on Industrial Electronics, vol. 68, no. 2, pp. 1275–1289, 2021.

- [21] K. C. Tseng, C. C. Huang, and C. A. Cheng, "A single-switch converter with high step- up gain and low diode voltage stress suitable for green power-source conversion," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 4, no. 2, pp. 363–372, 2016.

- [22] G. Wu, X. Ruan, and Z. Ye, "High step-up DC-DC converter based on switched capacitor and coupled inductor," IEEE Transactions on Industrial Electronics, vol. 65, no. 7, pp. 5572–5579, 2018.

- [23] Yuang-Shung Lee, Wei-Ting Hong and Tzu-Han Chou, "Multiphase High Gain Boost Converter with Switched-Capacitor and Coupled-Inductor", pp.320-325, 2013.

- [24] Y. Zheng and K. M. Smedley, "Interleaved high step-up converter integrating coupled inductor and switched capacitor for distributed generation systems," IEEE Transactions on Power Electronics, vol. 34, no. 8, pp. 7617–7628, 2019.

- [25] Y. Chen, Z. Lu, and R. Liang, "Analysis and design of a novel high-step-up DC/DC converter with coupled inductors," IEEE Transactions on Power Electronics, vol. 33, no. 1, pp. 425–436, 2018.